嬥揷幃姰懳SIT-2SJ18僷儚乕傾儞僾

2008/09/00

俽俷俶倄亅俀俽俰侾俉

丂偦偆偙偆偟偰偄傞偆偪偵丄姰懳夞楬偑敪昞偵側傝1994/09寧崋偵俀俽俲俇侽偺夞楬偑敪昞偵側傝傑偟偨丅 俀俽俰侾俉偺夞楬偼敪昞偝傟傑偣傫偱偟偨偑丄奣偹摨條偺夞楬偱僪儔僀僽偱偒傞偼偢偲摜傫偱崱夞惢嶌偲憡惉傝傑偟偨丅

丂傕偪傠傫僀儞僞乕僱僢僩忋偵傕挧愴偟偰偄傞曽傪尒庴偗傑偟偨偺偱嶲峫偵偟傑偟偨丅

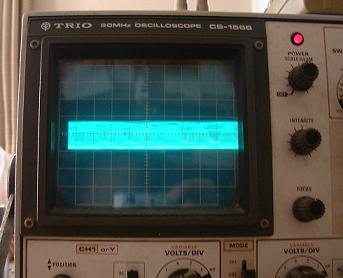

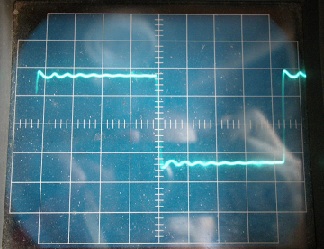

丂偝偰丄擖庤偟偨俿倰偺偽傜偮偒傪應掕偟偨偺偑師偺昞偱偡丅應掕忦審偼倁倓倱亖俀俀倁丄倁倗倓亖7.6倁偲偟偰 應掕偟偨暔偱偡丅

| 丂 | 侾 | 俀 | 俁 | 係 | 俆 | 俇 | 俈 | 俉 | 俋 | 侾侽 |

| 俬俢(mA) | 206 | 45 | 76 | 38 | 127 | 169 | 53 | 46 | 26 | 145 |

1975擭6寧崋偵俀俽俰侾俉偺掕奿偑嵹偭偰偄傑偟偨偺偱丄壓婰偺偲偍傝宖嵹偟偰偍偒傑偡丅

| 崁栚 | 婰崋 | 忦審 | 嵟彫 | 昗弨 | 嵟戝 | 扨埵 |

| 霓谳ス薨臉R揹棳 | Idgo | Vdg=-100Vs=0 | -0.1 | -100 | 兪A | |

| 罐澳幷抐揹棳 | Isgo | Vgs=-30Vds=0V | -0.1 | -100 | 兪A | |

| 递揹埑 | Von | Ig=-0.2A,Id=-3A, | -10 | V | ||

| 动牡虛d埑 | Vp | Vds=-60V,Id=-100mA | 7.5 | 18 | 25 | V |

| 擖椡梕検 | Ciss | Vgs=15V,Vds=0V,f=1MHz | 190 | pF | ||

| 幷抐廃攇悢 | fT | Vds=-20V,Id=-0.5A | 20 | MHz | ||

| 揹埑憹暆棪 | 兪 | Vds=-20V,Id=-1A,f=1kHz | 4 | |||

| 弌椡掞峈 | rD | Vds=-20V,Id=-1A,f=1kHz | 16 | 兌 | ||

| 崁栚 | 婰崋 | |

| 罐澳ツ挹草娫揹埑 | Vdgo | -170V |

| 罐澳タ敖娫揹埑 | Vsgo | -30V |

| 霓诓輷d棳 | Id | 5A |

| 罐澳揹棳 | Ig | -0.5A |

| 嫋梕揹椡懝幐 | Pt | 63W |

丂僇僢僩僆僼揹埑丒僆儞揹埑偺偳偪傜傪婎弨偵偡傟偽傛偄 偺偐暘偐傝傑偣傫偑丄梋桾傪尒偰僇僢僩僆僼揹埑傑偱僪儔僀僽偱偒傞傛偆偵峫偊傑偟偨丅偟偨偑偭偰俵俷俽亅 俥俤俿偵斾妑偟僪儔僀僽掞峈傪戝偒偔偟偰揹埑傪壱偖傛偆偵愝寁偟傑偡丅

丂師偵亄懁偺揹埑憹暆抜偺揹尮揹埑偵偮偄偰峫偊偰傒傞偲丄俀俽俰侾俉偺僾儔僗懁僪儔僀僽揹埑偼弌椡抜揹尮揹埑偐傜亄懁偵怗傟傞 偺偱丄偙偺揹埑偲俀俽俰俈俈偺僇僗僐乕僪夞楬偺揹埑傪忋忔偣偟偰寛傔傞偙偲偵側傝傑偡偑丄嵟掅偱傕俆侽倁偼 昁梫偲尒愊傕傟傑偡丅埲忋峫椂偟偰愝寁偟偨偺偑忋婰夞楬偱偟偨偑丄偙偺夞楬偱偼摦嶌偟傑偣傫偱偟偨丅

丂偲偙傠偱俀俽俰侾俉偼僶僀傾僗揹埑傪僜乕僗揹埑傛傝怺偔偡傞昁梫偑傞偨傔揹尮搳擖僞僀儈儞僌偵婥傪巊偆昁梫偑偁傝傑偡丅 傕偟揹埑憹暆抜傛傝弌椡抜偺傎偆偑憗偔棫偪忋偑偭偰偟傑偆偲夁戝側揹棳偑俥俤俿傊棳傟偰偟傑偄傑偡丅偲尵偆偙偲偱揹尮偺愝寁傕 偙傟傑偱埲忋偵婥傪巊傢側偗傟偽側傝傑偣傫丅崱傑偱偙偺僨僶僀僗傪庤偵擖傟側偑傜墑乆偲惢嶌偵妡偐傜側偐偭偨偺偼揹尮偺愝寁傪 偳偆偡傞偐丄擸傫偱偄偨偙偲偑堦斣偺棟桼偱偁偭偨傛偆偵巚偄傑偡丅

幚尡梡揹尮

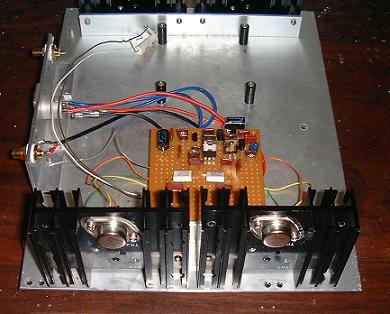

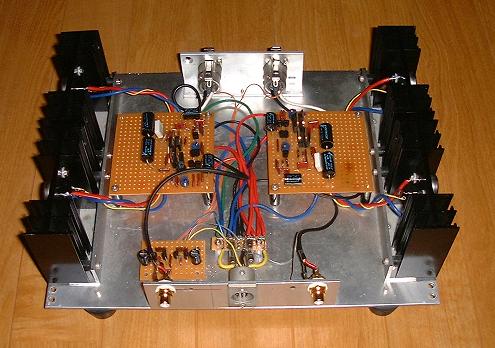

丂僩儔儞僗偼僞儞僑偺俙媺侾俆倂梡偺俙亅俁俆俽偱偡丅偙偺僩儔儞僗偵偼揔愗側揹埑憹暆抜梡偺 姫偒慄偑側偄偺偱丄揹埑憹暆抜梡偵俼僐傾偺僩儔儞僗傪暿偵梡堄偟傑偟偨丅揹埑偼俀俆倁R俆倁U侽倁丒俋侽倁傪愗傝懼偊偰弌偣傞傛偆偵 側偭偰偄傑偡丅僷儚乕傾儞僾偼婎傛傝僾儕傾儞僾偺幚尡偵傕巊偊傞傛偆偵偟傑偟偨丅

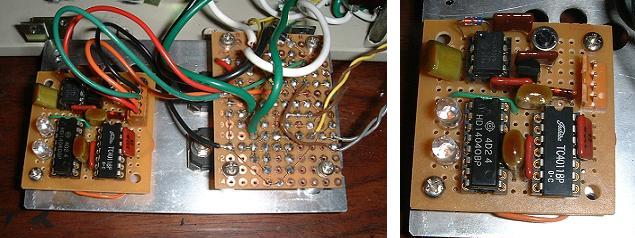

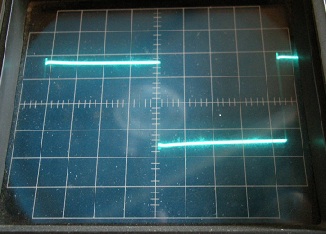

丂崱夞幚尡梡揹尮傪堦晹夵憿偟弌椡抜偵抶墑夞楬傪愝偗傑偟偨丅2006/11寧崋恀嬻娗幃僷儚乕傾儞僾偺抶墑夞楬傪偦偺傑傑堏怉偟偨傕偺偱偡丅

曐岇夞楬

丂側偍丄攝慄偼儐僯僶乕僒儖 婎斅傪巊偭偨偨傔丄俵俰偳偍傝偱偼側偔曄峏偟偰偄傑偡丅俴俤俢傪俀屄晅偗傑偟偨丅偙傟偵傛傝僇僂儞僞乕偺摦嶌忬嫷傪妋擣偱偒傑偡丅摦嶌傑偱 僀儔僀儔偣偢偵嵪傒傑偡丅

丂傑偨丄婰帠偺僷僞乕儞偼憡曄傢傜偢廋惓偑昁梫偱偟偨丅婥傪偮偗側偗傟偽側傜側偄偺偼 俬俠偺懌偺斣崋偑傑偭偨偔斀懳偺暔偑偁傝傑偡丅抶墑夞楬傪嶌偭偰巪偔偄偐側偐偭偨曽偼俬俠偺岦偒傪傕偆堦搙妋擣偝傟偨曽偑椙偄偐偲巚偄傑偡丅

傾儞僾婎斅

曅僠儍儞僱儖偺傒壖慻傒

崅廃攇偱敪怳

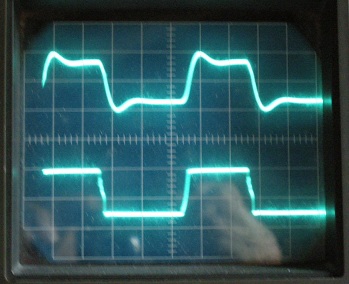

嵟廔夞楬

丂偙偺偲偒偼偳偆偟偨傕偺偐偲惉偡弍傕柍偔姰惉偵憜偓拝偗傞偙偲偑婋傇傑傟傑偟偨丅偦偺屻俀乣俁擔宱偭偰偄傠偄傠挷傋偰偄偨帪偵丄僱僢僩偱 俀俽俰侾俉傪巊偭偨傾儞僾傪敪昞偟偰偄偨椺傪尒偰丄巹偑帋嶌偟偨夞楬偲偺堘偄偵婥偑晅偒傑偟偨丅偦傟偼揹埑憹暆抜偲俀俽俰侾俉偺僎乕僩偺 愙懕売強偑亄亅懁偱斀懳偵側偭偰偄傞偙偲偱偟偨丅憗懍偦偺夞楬偵曄峏偟偨偲偙傠忋庤偔偄偒傑偟偨丅

丂側偍丄傾僀僪儕儞僌揹棳偼僎乕僩揹埑傪俉倁埵傑偱壓偘偰傕傎偲傫偳棳傟傑偣傫丅偟偨偑偭偰丄夞楬恾偺傛偆偵僶僀傾僗偺僎乕僩揹埑偼俈倁埵 尒偰偍偗偽椙偄傛偆側偺偱丄摉弶峫偊偰偄偨揹埑憹暆抜偺揹尮揹埑偼愝寁帪傛傝掅偔尒愊傕偭偰亄俆侽倁偐傜壓偘偰傕戝忎晇偺傛偆偵巚偄傑偡丅 傕偭偲傕崱偺偲偙傠寁夋偟偨揹埑偱壗偺栤戣傕側偄偺偱偙偺傑傑偵偟偰偍偒傑偡丅

丂忋婰偺棟桼偵傛傝俀俽俰侾俉偺偨傔偵侾俉倁傕偺崅偄僶僀傾僗揹埑偼昁梫側偄偨傔丄僎乕僩掞峈偱揹埑崀壓傪壱偑側偔偰傕椙偄偲峫偊丄俀俽俰侾俉偺 僶僀傾僗梡偺俁丏俋倠兌偼俀丏俈倠兌偵曄峏偟傑偟偨丅傑偨丄僀儞僺乕僟儞僗傪彮偟偱傕壓偘偰俥俤俿偺擖椡梕検偵懳張偟傛偆偲偺栚榑尒偱偡丅 偨偩偟丄偁傑傝壓偘傞偲傾儞僾慡懱偺棙摼偑壓偑傝婣娨検偑尭彮偡傞偙偲傕峫偊傜傟傑偡丅

丂俀俽俲俀侾係偺僜乕僗掞峈傕俀俽俰俈係偺揹棳傪俇丏侽倣俙慜屻偵偡傞偨傔偵曄峏偟傑偟偨丅

丂側偍丄弶抜偺僇僗僐乕僪俿倰傪俀俽俠侾俁俋俋偵偟偨偺偼懴埑傪峫偊偰偺偙偲偱偡偑丄揹埑傪壓偘傞偺偱偁傟偽俥俤俿傪巊偭偰傕戝忎晇偲 巚傢傟傑偡丅弶抜偺掕揹棳夞楬傪彍偄偰俥俤俿峔惉偲側傞偺偱丄偦偺曽偑俥俤俿偺壒偑惗偒偰偔傞偲巚傢傟傑偡丅

丂弶抜掕揹棳夞楬偵俀俶俆係俇俆傪巊偆偲姰慡俥俤俿峔惉偲側傝傑偡偑丄俀俶俆係俇俆偼擖庤擄偺忋偙偺俥俤俿偵媰偐偝傟偨偲偄偆榖傪椙偔暦偒傑偡丅 帠幚偙偺巹傕庤捝偄栚偵夛偭偰偄傞偙偲傕偁傝俿倰偵傛傞掕揹棳夞楬偲偟偰偄傑偡丅

丂俀俽俰侾俉偺僜乕僗掞峈侽丏係俈兌偼奜偟偰偟傑偄傑偟偨丅傾僀僪儕儞僌揹棳偼栺俀侽侽倣俙偵愝掕偟傑偟偨丅偄傠偄傠愄偺俵俰側偳挷傋偨偲偙傠 偙偺埵偺傾僀僪儕儞僌揹棳偼棳偟偰偍偄偨曽偑椙偄偲偺寢榑偵払偟傑偟偨丅側偍丄奜偟偰偟偽傜偔傾僀僪儕儞僌揹棳偺條巕傪尒傑偟偨偑丄 梋桾偺曻擬婍傪巊偭偨偙偲傕偁偭偰偐揹棳偑憹偊傞條巕偼旝恛傕柍偄傛偆偱偡丅

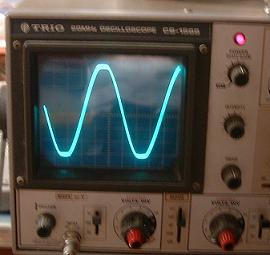

弌椡攇宍

姰惉

2013/07/06

姰惉偲巚偄偒傗丄敪怳偟偰偄傑偟偨両

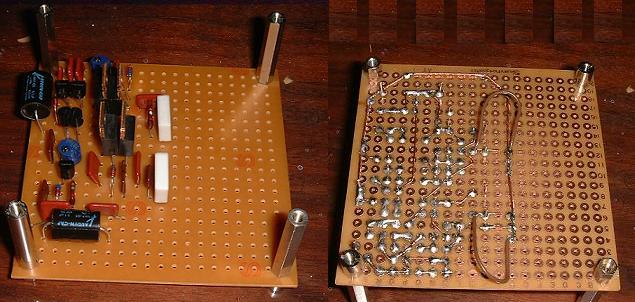

姰惉偟偨偺偼2008偛傠偱偟偨偑丄偦偺帪偵偼傑偩僗僺乕僇乕偵宷偄偱壒傪弌偟偰偄傑偣傫偱偟偨丅崱寧偵擖偭偰僗僺乕僇偵宷偄偱曽宍攇傪擖椡偡傞偲, 敪怳偟偰偄傞偙偲偑敾柧偟傑偟偨丅偙偺偨傔埵憡曗惓夞楬傪堦晹偄偠偭偰敪怳偑巭傑傞傛偆偵偟傑偟偨丅偦偺夞楬偑偙傟偱偡丅 傑偢弶抜偵620兌亄510PF傪丄偝傜偵弌椡偵10兌亄0.1兪F傪丄僷儚乕抜偺揹尮偵僶僀億乕儔偺揹夝僐儞10兪F傪宷偓傑偟偨丅

丂婎斅偺昞偼嵍懁偺偲偍傝丄弌椡偵偼愄偺巜掕偱AUDYN-CAP偺僼僀儖儉0.1兪F丄10兌偺掞峈偼僕儍儞僋敔偁偭偨丠僗働儖僩儞丄僷儚乕抜偺揹尮偵偼10兪F丄

僆乕僨僆梡偱偼側偄擔杮働儈僐儞偺柍嬌惈揹夝僐儞僨儞僒乕丄挷払愭偼RS僆儞儔僀儞偩偭偨偲巚偄傑偡丅

丂婎斅偺昞偼嵍懁偺偲偍傝丄弌椡偵偼愄偺巜掕偱AUDYN-CAP偺僼僀儖儉0.1兪F丄10兌偺掞峈偼僕儍儞僋敔偁偭偨丠僗働儖僩儞丄僷儚乕抜偺揹尮偵偼10兪F丄

僆乕僨僆梡偱偼側偄擔杮働儈僐儞偺柍嬌惈揹夝僐儞僨儞僒乕丄挷払愭偼RS僆儞儔僀儞偩偭偨偲巚偄傑偡丅婎斅偺棤偼塃懁偺偲偍傝埵憡曗惓偺11倫俥偼庢傝彍偄偰偟傑偄傑偟偨丄僗僥僢僾宆埵憡曗惓偼婎斅偺棤偵偠偐晅偗620兌亄510倫俥偱偡丅嵟弶1丏2k兌埵偐傜 巒傔傑偟偨偑偆傑偔峴偒傑偣傫偱偟偨丅偙偺抣偱曽宍攇墳摎傪尒傞尷傝敪怳偼偟偰偄側偄偺偱栤戣偼側偝偦偆偱偡丅

丂3擭埲忋慜偵惢嶌傪奐巒偟丄傗偭偲壒偑弌偰SIT偺壒傪妋擣偱偒傑偟偨丅偟偐偟丄崱偼傕偆擖庤偱偒側偄偺偱敪昞偡傞堄枴傕側偄偐傕丅